## HT7L5820/HT7L5821 Integrated PFC and Quasi-Resonant Current Mode PWM Controller

### Features

- Integrated Transition Mode (TM) PFC controller and Quasi-Resonant (QR) flyback controller

- Wide AC input range from  $85V_{AC}$  to  $265V_{AC}$

- Integrated 650V JFET quick high voltage start-up

- Integrated THD PFC stage optimiser

- · Brown-out and brown-in protection

- Internal accurate feedback reference voltage:  $\pm 2\%$

- Internal 9.6ms PWM soft-start

- High/Low line over-power compensation

- FB pin protection (Auto Recovery)

- Over-power and overload protection

- Short-circuit protection

- Open-loop protection

- External triggering and adjustabe over-temperature protection RT Pin

- VCC pin OVP latched

- Internal over-temperature shutdown  $140^{\circ}C$

- 16-pin NSOP package

### Applications

- AC/DC NB adapters

- Open-frame SMPS

- Battery chargers

- General LED lighting applications

- · Industrial, commercial, and residential fixtures

### **General Description**

The HT7L5820/HT7L5821 is highly integrated device which includes a Power Factor Correction controller and quasi-resonant flyback controller. The high level of functional integration provides the means for very cost-effective designs with a minimum of external components.

In the PFC stage the device uses a transition mode to provide a regulated output voltage with low system costs, low harmonic distortion and high power factor. For QR flyback the device provides higher efficiencies and lower EMI when compared with conventional PWM systems.

The device also includes a range of features to protect the controller from fault conditions. These include secondary side open-loop and over-current protection, VCC pin over-voltage protection, DET pin overvoltage for output over-voltage protection, brownin/out AC input voltage, internal over-temperature shutdown and adjustable over-temperature protection using the RT pin with an external NTC resistor.

### **Selection Table**

| Part No.   |                    | HT7L5820          | HT7L5821 |

|------------|--------------------|-------------------|----------|

| Protection | Internal OTP       |                   |          |

|            | RT Pin OTP         | Auto-<br>Recovery | Latched  |

| Mode       | RT Pin Triggering  |                   | Lateneu  |

|            | Output Voltage OVP |                   |          |

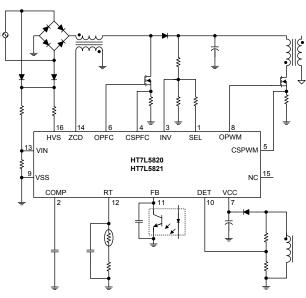

### **Application Circuits**

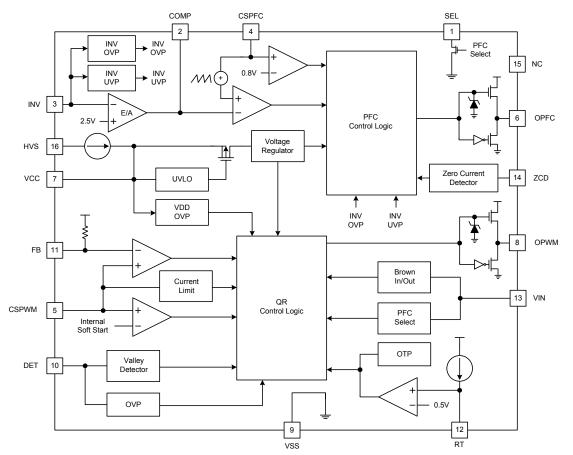

### **Block Diagram**

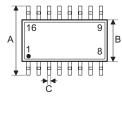

## **Pin Assignment**

|                   |           | _      |    |       |  |  |  |

|-------------------|-----------|--------|----|-------|--|--|--|

| SEL 🗆             | 1         | $\cup$ | 16 | ⊒ нvs |  |  |  |

| COMP 🗆            | 2         |        | 15 | ⊐ NC  |  |  |  |

| INV 🗆             | 3         |        | 14 | 🗆 ZCD |  |  |  |

| CSPFC             | 4         |        | 13 | □ VIN |  |  |  |

| CSPWM             | 5         |        | 12 | 🗆 RT  |  |  |  |

| OPFC 🗆            | 6         |        | 11 | 🗆 FB  |  |  |  |

| VCC 🗆             | 7         |        | 10 | DET   |  |  |  |

| OPWM 🗆            | 8         |        | 9  | ⊐ vss |  |  |  |

| HT7L5820/HT7L5821 |           |        |    |       |  |  |  |

| 16 NSOP-A         |           |        |    |       |  |  |  |

|                   | IO NOUP-A |        |    |       |  |  |  |

### **Pin Description**

| Pin No. | Symbol | Description                                                                     |

|---------|--------|---------------------------------------------------------------------------------|

| 1       | SEL    | PFC output selected pin                                                         |

| 2       | COMP   | PFC compensation pin, a capacitor should be placed between COMP and VSS         |

| 3       | INV    | Voltage sense for PFC output, regulation voltage is 2.5V                        |

| 4       | CSPFC  | Current sense pin. A resistor is connected to sense the PFC MOSFET current      |

| 5       | CSPWM  | Current sense pin. A resistor is connected to sense the Flyback MOSFET current  |

| 6       | OPFC   | Gate drive output to drive the external MOSFET for PFC                          |

| 7       | VCC    | Power supply pin                                                                |

| 8       | OPWM   | Gate drive output to drive the external MOSFET for Flyback                      |

| 9       | VSS    | Ground pin                                                                      |

| 10      | DET    | Zero-current detect pin for Flyback                                             |

| 11      | FB     | Voltage feedback pin for Flyback. Connect a photo-coupler for system regulation |

| 12      | RT     | External protection triggering                                                  |

| 13      | VIN    | Sense input for mains voltage                                                   |

| 14      | ZCD    | Zero-current detect pin for PFC                                                 |

| 15      | NC     | No connection                                                                   |

| 16      | HVS    | HVS pin is connected to the AC line voltage through a resistor                  |

# **Absolute Maximum Ratings**

| Parameter                                 | Value                | Unit |

|-------------------------------------------|----------------------|------|

| VCC Supply Voltage                        | -0.3 to 30           | V    |

| HVS Voltage                               | -0.3 to 650          | V    |

| SEL, COMP, INV, CSPFC, CSPWM, FB, RT, VIN | -0.3 to 6            | V    |

| Maximum Current at ZCD, DET               | 3 (source), 3 (sink) | mA   |

| Operating Junction Temperature            | -40 to 150           | °C   |

| Storage Temperature Range                 | -55 to 150           | °C   |

| Maximum Junction Temperature              | 150                  | °C   |

# **Recommended Operating**

| Parameter                     | Value      | Unit |

|-------------------------------|------------|------|

| Operating Ambient temperature | -40 to 105 | °C   |

### **Electrical Characteristics**

| Symbol                  | Parameter                                                                      | Conditions                                                                                  | Min.   | Тур.   | Max.   | Unit |

|-------------------------|--------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--------|--------|--------|------|

| Vcc Sectio              | n                                                                              |                                                                                             |        | 51     |        |      |

| VOP                     | Continuous Operation Voltage                                                   |                                                                                             | _      | _      | 25     | V    |

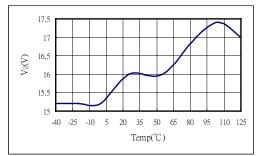

| Vcc-on                  | Turn-On Threshold Voltage                                                      |                                                                                             | 15     | 16.5   | 18     | V    |

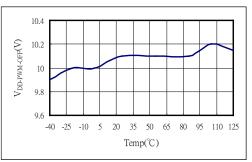

| V <sub>CC-PWM-OFF</sub> | PWM Off Threshold Voltage                                                      |                                                                                             | 9      | 10     | 11     | V    |

| Vcc-off                 | Turn-Off Threshold Voltage                                                     |                                                                                             | 7      | 8      | 9      | V    |

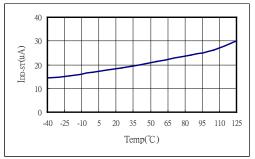

| IDD-ST                  | Startup Current                                                                | V <sub>CC</sub> =V <sub>CC-ON</sub> -0.16V,<br>gate open                                    | _      | 20     | _      | μA   |

| I <sub>DD-OP</sub>      | Operating Current                                                              | V <sub>cc</sub> =15V, OPFC,<br>OPWM=100kHz,<br>C <sub>L-PFC</sub> , C <sub>L-PWM</sub> =2nF |        |        | 10     | mA   |

| DD-GREEN                | Green Mode Operating Supply Current (Average)                                  | V <sub>CC</sub> =15V, C <sub>L-PWM</sub> =2nF<br>OPWM=450Hz                                 | _      | 5.5    | _      | mA   |

| DD-PWM-OFF              | Operating Current at PWM-Off Phase                                             | V <sub>CC</sub> =V <sub>CC-PWM-OFF</sub> - 0.5V                                             | 70     | 120    | 170    | μA   |

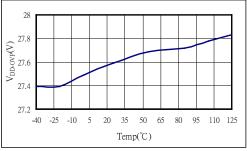

| Vcc-ovp                 | V <sub>cc</sub> Over-Voltage Protection (Latch-Off)                            | _                                                                                           | 26     | 28     | 30     | V    |

| tvcc-ovp                | V <sub>cc</sub> OVP Debounce Time                                              | _                                                                                           | 100    | 150    | 200    | μs   |

| IDD-LATCH               | V <sub>CC</sub> Over-Voltage Protection Latch-Up Holding Current               | V <sub>cc</sub> =7.5V                                                                       | _      | 120    | _      | μA   |

| HVS Start               | up Current Source Section                                                      |                                                                                             |        |        |        |      |

| V <sub>HVS-MIN</sub>    | Minimum Startup Voltage on HVS Pin                                             | _                                                                                           | _      | _      | 50     | V    |

|                         | Supply Current Drown from LN/S Din                                             | V <sub>AC</sub> =90V (V <sub>DC</sub> =120V),<br>V <sub>CC</sub> =0V                        | 1.3    | _      | _      | mA   |

| HVS                     | Supply Current Drawn from HVS Pin                                              | HVS=500V,<br>V <sub>CC</sub> =V <sub>CC-OFF</sub> +1V                                       | _      | 8      | _      | μA   |

| VIN and S               | EL Section                                                                     |                                                                                             |        |        |        |      |

| V <sub>VIN-UVP</sub>    | Threshold Voltage for AC Input Under-Voltage Protection                        | _                                                                                           | 0.85   | 0.9    | 0.95   | V    |

| V <sub>VIN-RE-UVP</sub> | Under-Voltage Protection Reset Voltage (for Startup)                           | _                                                                                           | 1.2    | 1.25   | 1.3    | V    |

| t <sub>vin-uvp</sub>    | Under-Voltage Protection Debounce Time<br>(No Need at Startup and Hiccup Mode) |                                                                                             | 70     | 120    | 170    | ms   |

| V <sub>VIN-SEL-H</sub>  | High VVIN Threshold for SEL Comparator                                         | SEL ground                                                                                  | 2.45   | 2.5    | 2.55   | V    |

| V <sub>VIN-SEL-L</sub>  | Low V <sub>VIN</sub> Threshold for SEL Comparator                              | SEL open                                                                                    | 2.25   | 2.3    | 2.35   | V    |

| t <sub>SEL</sub>        | SEL-Enable Debounce Time                                                       | _                                                                                           | 70     | 120    | 170    | ms   |

| V <sub>SEL-OL</sub>     | Output Low Voltage of SEL Pin                                                  | lo=0.1mA                                                                                    |        | 1      | _      | V    |

| t <sub>on-max-PFC</sub> | PFC Maximum On Time                                                            | CSPFC=0v,COMP=5.5V                                                                          | 32     | 40     | 48     | μs   |

| PWM STA                 | GE                                                                             |                                                                                             |        |        |        |      |

| Av                      | Input-Voltage to Current Sense Attenuation <sup>(note)</sup>                   | $\begin{array}{l} A_{V} = \Delta V_{CS} / \Delta V_{FB}, \\ 0 < V_{CS} < 0.9 V \end{array}$ | 1/2.75 | 1/3.00 | 1/3.25 | V    |

| Z <sub>FB</sub>         | Input Impedance <sup>(note)</sup>                                              | FB>V <sub>G</sub>                                                                           | _      | 20     | _      | kΩ   |

| loz                     | Bias Current                                                                   | FB=Voz                                                                                      | _      | 0.2    | _      | mA   |

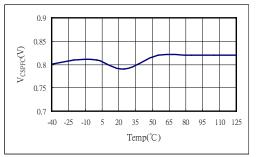

| V <sub>oz</sub>         | Zero Duty-cycle Input Voltage                                                  | _                                                                                           | 0.7    | 0.9    | 1.1    | V    |

| V <sub>FB-OLP</sub>     | Open-Loop Protection Threshold Voltage                                         | _                                                                                           | 3.9    | 4.2    | 4.5    | V    |

| t <sub>FB-OLP</sub>     | The Debounce Time for Open Loop Protection                                     |                                                                                             | 20     | 60     | 100    | ms   |

| t <sub>ss</sub>         | Internal Soft-Start Time <sup>(note)</sup>                                     | _                                                                                           |        | 9.6    | _      | ms   |

| Symbol                | Parameter                                                                                                      | Conditions                                           | Min. | Тур. | Max. | Unit |

|-----------------------|----------------------------------------------------------------------------------------------------------------|------------------------------------------------------|------|------|------|------|

|                       | VP and Valley Detection Section                                                                                |                                                      |      |      |      |      |

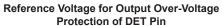

| V <sub>DET-OVP</sub>  | Comparator Reference Voltage                                                                                   | _                                                    | 2.45 | 2.5  | 2.55 | V    |

| t <sub>DET-OVP</sub>  | Output OVP Debounce Time                                                                                       | _                                                    | 100  | 170  | 240  | μs   |

| VDET-HIGH             | Upper Clamp Voltage                                                                                            | I <sub>DET</sub> =1mA                                | _    | 5.7  | _    | V    |

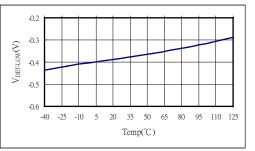

| VDET-LOW              | Lower Clamp Voltage                                                                                            | I <sub>DET</sub> =-1mA                               |      | -0.4 | _    | V    |

| tvalley-delay         | Delay Time from Valley Signal Detected to Output Turn-on <sup>(note)</sup>                                     | _                                                    | 150  | 200  | 250  | ns   |

| toff-bnk              | Leading-Edge Blanking Time for DET-OVP<br>(2.5V) and Valley Signal when PWM MOS<br>Turns Off <sup>(note)</sup> | _                                                    | 3    | 4    | 5    | μs   |

| t <sub>TIME-OUT</sub> | Time-Out After toff-MIN                                                                                        | _                                                    | 5    | 6    | 7    | μs   |

| PWM Osci              | llator Section                                                                                                 | 1                                                    |      |      |      |      |

| ton-max-pwm           | Maximum On Time                                                                                                | _                                                    | 38   | 46   | 54   | μs   |

| +                     | Minimum Off Time                                                                                               | V <sub>FB</sub> ≥V <sub>N</sub>                      | 7    | 8.5  | 10   | μs   |

| toff-min              |                                                                                                                | V <sub>FB</sub> =V <sub>G</sub>                      | 31   | 36   | 41   | μs   |

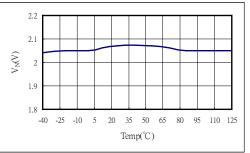

| V <sub>N</sub>        | Beginning of Green-On Mode at FB Voltage Level                                                                 | _                                                    | 1.95 | 2.1  | 2.25 | V    |

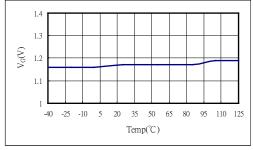

| V <sub>G</sub>        | Beginning of Green-Off Mode at FB Voltage Level                                                                | _                                                    | 1.05 | 1.2  | 1.35 | V    |

| ΔV <sub>G</sub>       | Hysteresis for Beginning of Green-Off Mode at FB Voltage Level                                                 | _                                                    | _    | 0.1  | _    | V    |

|                       | Threaded Welters on ED Dia to Diaghte DEC                                                                      | n to Disable PFC SEL open SEL ground                 | 1.5  | 1.55 | 1.6  | V    |

| VCTL-PFC-OFF          | hreshold Voltage on FB Pin to Disable PFC                                                                      | 1.5                                                  | 1.55 | 1.6  | V    |      |

| M                     | Threshold Voltage on ED Din to Enchla DEC                                                                      | SEL open                                             | 1.85 | 1.9  | 1.95 | V    |

| VCTL-PFC-ON           | Threshold Voltage on FB Pin to Enable PFC                                                                      | SEL ground                                           | 1.7  | 1.75 | 1.8  | V    |

| t <sub>PFC-OFF</sub>  | PFC Disable Debounce Time to Disable PFC                                                                       | PFC status from on to off                            | 400  | 600  | 800  | ms   |

| t <sub>PFC-ON</sub>   | PFC Disable Debounce Time to Enable PFC                                                                        | PFC status from off to on                            | —    | 150  | —    | μs   |

| tstarter-pwm          | Start Timer (Time-Out Timer)                                                                                   | $V_{FB} < V_G$                                       | 2    | 2.5  | 3    | ms   |

| PWM Outp              | out Section                                                                                                    |                                                      |      |      |      |      |

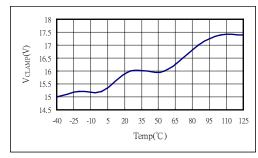

| VCLAMP                | PWM Gate Output Clamping Voltage                                                                               | Vcc=25V                                              | 16   | 17.5 | 19   | V    |

| Vol                   | PWM Gate Output Voltage Low                                                                                    | V <sub>cc</sub> =15V, I <sub>o</sub> =100mA          | _    |      | 1.5  | V    |

| V <sub>OH</sub>       | PWM Gate Output Voltage High                                                                                   | Vcc=15V, Io=100mA                                    | 8    | —    | _    | V    |

| t <sub>R</sub>        | PWM Gate Output Rising Time                                                                                    | C <sub>L</sub> =3nF, V <sub>CC</sub> =12V,<br>20~80% | —    | 80   | 110  | ns   |

| t⊧                    | PWM Gate Output Falling Time                                                                                   | C∟=3nF, V <sub>CC</sub> =12V,<br>20~80%              | —    | 40   | 70   | ns   |

| Current Se            | ense Section                                                                                                   |                                                      |      |      |      |      |

| t <sub>PD</sub>       | Delay to Output                                                                                                | _                                                    |      | 70   | 200  | ns   |

| V/                    | The Limit Voltage on CSPWM Pin for Over                                                                        | I <sub>DET</sub> <75µА, Та=25°С                      | 0.82 | 0.85 | 0.88 | V    |

| VLIMIT                | Power Compensation                                                                                             | I <sub>DET</sub> =550µА, Та=25°С                     | 0.37 | 0.4  | 0.43 | V    |

| Maria                 | Slong Componentian <sup>(note)</sup>                                                                           | ton=45µs                                             | _    | 0.3  | _    | V    |

| VSLOPE                | Slope Compensation <sup>(note)</sup>                                                                           | t <sub>on</sub> =0µs                                 |      | 0    | _    | V    |

| t <sub>on-bnk</sub>   | Leading-Edge Blanking Time                                                                                     | —                                                    |      | 300  | _    | ns   |

| Vcs-floating          | CSPWM Pin Floating V <sub>CSPWM</sub> Clamped High Voltage                                                     | CSPWM pin floating                                   | _    | 3.75 | _    | V    |

| t <sub>cs-н</sub>     | The Delay Time Once CS Pin Floating                                                                            | CSPWM pin floating                                   |      | 150  | _    | μs   |

| Symbol                | Parameter                                               | Conditions                                                                                | Min.  | Тур.  | Max.  | Unit |

|-----------------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------|-------|-------|-------|------|

| RT Pin Ov             | er-Temperature Protection Section                       |                                                                                           |       |       |       |      |

| Тотр                  | Internal Threshold Temperature for OTP (note)           | _                                                                                         | 125   | 140   | 155   | °C   |

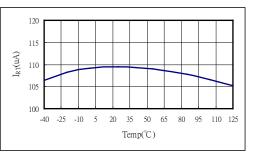

| I <sub>RT</sub>       | Internal Source Current of RT Pin                       | _                                                                                         | 96    | 107   | 118   | μA   |

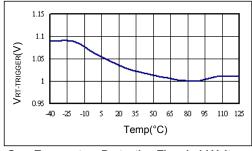

| VRT-TRIGGER           | Protection triggering Voltage                           | _                                                                                         | 0.95  | 1     | 1.05  | V    |

| VRT-OTP-LEVEL         | Threshold Voltage for Two-level Debounce<br>Time        | _                                                                                         | 0.45  | 0.5   | 0.55  | V    |

| t <sub>RT-OTP-H</sub> | Debounce Time for OTP                                   | _                                                                                         | _     | 10    | _     | ms   |

| t <sub>RT-OTP-L</sub> | Debounce Time for Externally Triggering                 | VRT <vrt-otp-level< td=""><td>70</td><td>100</td><td>130</td><td>μs</td></vrt-otp-level<> | 70    | 100   | 130   | μs   |

| PFC Stage             | )                                                       | 1                                                                                         |       |       |       | -    |

| Voltage Er            | ror Amplifier Section                                   |                                                                                           |       |       |       |      |

| Gm                    | Transconductance <sup>(note)</sup>                      | _                                                                                         | _     | 150   | _     | μS   |

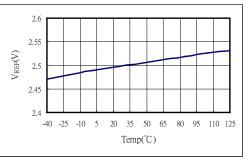

| Vref                  | Feedback Comparator Reference Voltage                   | _                                                                                         | 2.465 | 2.5   | 2.535 | V    |

| . ,                   |                                                         | SEL open                                                                                  | 2.65  | 2.70  | 2.75  | V    |

| V <sub>INV-OVP</sub>  | Over Voltage Protection for INV Input                   | SEL ground                                                                                | 2.575 | 2.625 | 2.675 | V    |

| VINV-UVP              | Under-Voltage Protection for INV Input                  | _                                                                                         | 0.25  | 0.35  | 0.45  | V    |

| t <sub>INV-UVP</sub>  | Under-Voltage Protection Debounce Time                  | _                                                                                         | 30    | 60    | 90    | μs   |

| V <sub>INV-BO</sub>   | PWM and PFC Off Threshold for Brownout<br>Protection    | _                                                                                         | 1.15  | 1.2   | 1.25  | V    |

| V <sub>сомр-во</sub>  | Limited Voltage on COMP Pin for Brownout<br>Protection  | _                                                                                         | _     | 1.6   | _     | V    |

| V <sub>COMP</sub>     | Comparator Output High Voltage                          |                                                                                           | 5.5   | _     | 6.5   | V    |

| Voz                   | Zero Duty Cycle Voltage on COMP Pin                     | _                                                                                         | 0.65  | 0.7   | 0.75  | V    |

|                       | Comparator Output Source Current                        | V <sub>INV</sub> =2.3V, V <sub>COMP</sub> =1.5V                                           |       | 30    | _     | μA   |

| COMP                  | Comparator Output Sink Current                          | VINV=2.7V, VCOMP=5V                                                                       | _     | 30    | _     | μA   |

| PFC Curre             | ent Sense Section                                       | 1                                                                                         |       |       |       |      |

| V <sub>CSPFC</sub>    | Threshold Voltage for Peak Current Cycle-by-Cycle Limit | V <sub>COMP</sub> =5V                                                                     | _     | 0.8   | _     | V    |

| t <sub>PD</sub>       | Propagation Delay                                       | _                                                                                         | _     | 180   | 300   | ns   |

| t <sub>LEB</sub>      | Leading Edge Blanking Time                              | _                                                                                         | _     | 200   |       | ns   |

| PFC Zero              | Current Detection Section                               | 1                                                                                         |       |       |       |      |

| V <sub>ZCD</sub>      | Input Threshold Voltage Rise Edge                       | V <sub>ZCD</sub> increasing                                                               | _     | 1.4   |       | V    |

| V <sub>ZCD-HYST</sub> | Threshold Voltage Hysteresis                            | V <sub>ZCD</sub> decreasing                                                               |       | 0.7   |       | V    |

| Vzcd-HIGH             | Upper Clamp Voltage                                     | I <sub>ZCD</sub> =1mA                                                                     | _     | 5.7   | _     | V    |

| Vzcd-low              | Lower Clamp Voltage                                     | I <sub>ZCD</sub> =-1mA                                                                    | _     | -0.4  | _     | V    |

| t <sub>DELAY</sub>    | Maximum Delay from ZCD to Output Turn-On                | V <sub>COMP</sub> =5V, f <sub>S</sub> =60kHz                                              | 100   | _     | 200   | ns   |

| trestart-pfc          | Restart Time                                            | _                                                                                         | _     | 190   | _     | μs   |

| t <sub>імнів</sub>    | Inhibit Time<br>(Maximum Switching Frequency Limit)     | V <sub>COMP</sub> =5V                                                                     | _     | 1     | _     | μs   |

| PFC Outpu             |                                                         | 1                                                                                         |       |       |       |      |

| Vz ·                  | PFC Gate Output Clamping Voltage                        | Vcc=25V                                                                                   | 16    | 17.5  | 19    | V    |

| Vol                   | PFC Gate Output Voltage Low                             | V <sub>cc</sub> =15V, I <sub>o</sub> =100mA                                               | _     | _     | 1.5   | V    |

| Vон                   | PFC Gate Output Voltage High                            | V <sub>cc</sub> =15V, I <sub>o</sub> =100mA                                               | 8     | _     | _     | V    |

| t <sub>R</sub>        | PFC Gate Output Rising Time                             | C <sub>L</sub> =3nF, V <sub>CC</sub> =12V,<br>20~80%                                      | _     | 80    | 110   | ns   |

| t⊧                    | PFC Gate Output Falling Time                            | C <sub>L</sub> =3nF, V <sub>CC</sub> =12V,<br>20~80%                                      | _     | 40    | 70    | ns   |

Note: Guaranteed by design.

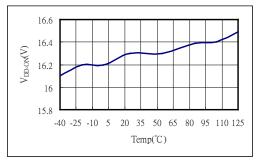

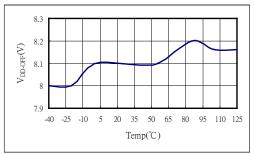

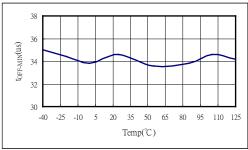

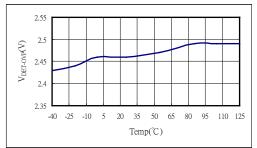

### **Typical Performance Characteristics**

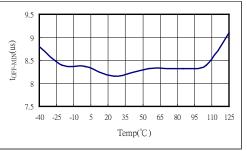

**Turn-On Threshold Voltage**

**Turn-Off Threshold Voltage**

PFC Gate Output Clamping Voltage

**PWM Off Threshold Voltage**

VCC Over-Voltage Protection Threshold

PFC Output Feedback Reference Voltage

PFC Peak Current Limit Voltage

PWM Gate Output Clamping Voltage

Beginning of Green-Off Mode at VFB

PWM Minimum Off-Time for VFB=VG

Beginning of Green-On Mode at VFB

PWM Minimum Off-Time for VFB > VN

Internal Source Current of RT Pin

Over Temperature Protection Threshold Voltage of RT Pin

### **Functional Description**

#### **PFC Stage**

#### **Error Amplifier**

The PFC error amplifier is used for regulating the PFC output voltage. The error amplifier input is the INV pin and it is connected to a resistor divider from the PFC output. The error amplifier input voltage is compared with an internal reference voltage of 2.5V to make the error amplifier source or sink current to charge and discharge its output capacitor. The capacitor voltage will determine the on-time of the PFC controller to regulate the output voltage. The sink and source capability of the error amplifier is approximately 30uA during normal the operation and the typical transconductance value is 150µS.

#### **Dynamic Response**

The PFC dynamic response is very slow because of the PFC voltage loop low frequency bandwidth. The device provides an enhanced dynamic response for the PFC loop by detecting the feedback voltage on the INV pin. Whenever the INV voltage is lower than the reference value 2.3V, it will increase the error amplifier transconductance and in turn increase the PFC duty cycle directly. This change in duty cycle bypasses the slow change of the COMP voltage and thus results in a fast dynamic response for the PFC stage.

#### **ZCD Pin**

The device performs zero current detection by using an auxiliary winding on the PFC boost inductor. During normal operation, when the PFC MOS is switched off, the stored energy in the PFC boost inductor will release its energy to the output. The voltage on the ZCD pin decreases as the stored energy in the PFC boost inductor is released to the output. When the ZCD pin voltage is lower than 0.7V, the internal ZCD comparator is triggered and a PFC gate signal is generated. If no triggering signal is detected on the ZCD pin, the device will generate a restart signal 190µs after the last PFC gate signal. The maximum and minimum voltage of the ZCD pin is internally clamped to 5.7V and 0V respectively

#### SEL Pin

A built-in low voltage switch can be turned on or off according to VIN voltage level. The drain pin of this internal switch is connected to the SEL pin.

#### Brown-in/out Protection – VIN Pin

The device features brown-in/out protection using AC voltage detection. The VIN pin is used to detect the AC input voltage using a resistor divider. As the AC voltage drops and the  $V_{VIN}$  voltage drops below 0.9V for 100ms, the UVP protection function is activated and the COMP pin voltage is clamped to around 1.6V. Since a lower COMP voltage results in a reduced PFC on-time, the energy concentration is limited and therefore the PFC output voltage decreases. When the INV pin is lower than 1.2V, the device turns off all PFC and PWM switching operations and the  $V_{CC}$  voltage enters the hiccup mode. Not until the  $V_{VIN}$  voltage increases beyond 1.25V (typical) and  $V_{CC}$  reaches its turn-on voltage again will the PWM and PFC gate signals be generated.

#### Peak Current Limiting - CSPFC Pin

The CSPFC pin is used to sense the PFC switch current. During normal PFC operation, the voltage on the CSPFC pin is compared with a threshold voltage of 0.8V using the internal comparator. When the CSPFC pin voltage is greater than the threshold voltage, the PFC switch will be turned off immediately. The current-sense resistor is adjustable to determine the PFC switch peak current.

#### **Output Voltage OVP and UVP – INV Pin**

Over-voltage and under-voltage protection functions are integrated into the device for the PFC stage. Both are detected and determined using the INV pin voltage. The OVP or UVP circuit is activated to stop PFC switching operations immediately when the INV pin voltage is greater than 2.65V or less than 0.35V. In addition, the de-bounce time of the OVP and UVP is set to about 70 $\mu$ s to avoid overshoot or abnormal conditions.

#### **QR Flyback Stage**

#### Startup Current – HVS Pin

For startup purposes the HVS pin is connected to the AC line input through a resistor. Using an integrated high-voltage startup circuit, the device provides a high current to charge the external VCC capacitor to reduce the controller's startup time. To reduce power consumption, when the VCC voltage exceeds the turn-on voltage and enters normal operation, this high voltage startup circuit will be switched off to avoid power losses due to power consumption in the startup resistor.

#### Under-Voltage Lockout (UVLO) – VCC Pin

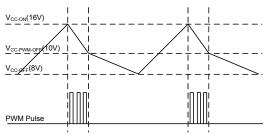

The turn-on, PWM-off and turn-off thresholds are fixed internally at 16V/10V/8V, respectively. During startup, the hold-up capacitor ( $V_{CC}$  cap.) is charged by the HV startup current until the  $V_{CC}$  voltage reaches the turn-on voltage. The hold-up capacitor continues to supply  $V_{CC}$  until energy can be delivered from the auxiliary winding. During this startup process,  $V_{CC}$  must not drop below  $V_{CC \text{ PWM-OFF}}$ . This UVLO hysteresis window ensures that hold-up capacitor is suitable for supplying  $V_{CC}$  during startup. The following figure shows the  $V_{CC}$  waveform in the hiccup mode.

Vcc during Hiccup Mode Operation

#### Valley Detection – DET Pin

The DET pin is connected to an auxiliary winding of the transformer using divider resistors. During the PWM off time, when the transformer inductor current discharges to zero, the transformer inductor and parasitic capacitors of the PWM switch start to resonate concurrently. As the drain voltage on the PWM switch falls, the voltage on the auxiliary winding V<sub>AUX</sub> decreases as well. Then, the internal DET comparator detects the valley voltage of the switching waveform to achieve valley voltage switching. This ensures QR operation, minimises switching losses and reduces EMI. The maximum and minimum voltage of the DET pin is internally clamped to 5.7V and -0.4V respectively.

#### Green-Mode and PFC On/Off Control – FB Pin

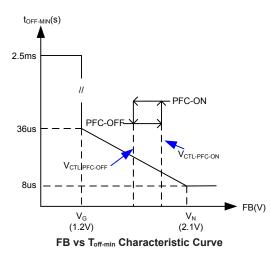

A Green Mode mechanism is adopted to reduce switching losses in the power system under conditions of light load. The device uses a linear off-time modulation to decrease switching frequency according to the FB pin voltage. The following figure shows the FB versus t<sub>OFF-MIN</sub> characteristic curve. As FB pin Voltage is lower than  $V_N$  (2.1V), the toff-min time increases with lower FB pin voltage. The valley voltage detection signal does not activate until the toFF-MIN time finishes which extends valley voltage switching during DCM operation and reduces switching losses to obtain higher conversion efficiencies. In addition, in order to reduce the standby power under conditions of no load or very light-load, the FB pin voltage is also used to control the PFC on/off operation. As the FB voltage falls below the V<sub>CTL-PFC-OFF</sub> threshold voltage the controller will stop PFC switching until the FB pin voltage returns to V<sub>CTL-PFC-ON</sub>.

# High/Low Line Over-Power Compensation – DET Pin

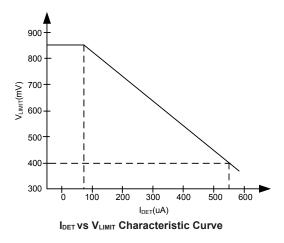

The power delivered by a flyback power supply is proportional to the square of the peak current during QR control. However, due to the inherent propagation delay of the logic, the actual peak current is higher for a high input voltage than for a low input voltage. This results in a significant difference between the maximum output power delivered by the power supply. To compensate for this variation for a universal input range, the DET pin produces an offset voltage to compensate the threshold voltage of the peak current limit.

This offset voltage is generated by sensing the current drawn from the DET pin when the power switch turns on. The following figure shows the  $I_{\rm DET}$  versus  $V_{\rm LIMIT}$  characteristic curve.

#### Leading Edge Blanking – LEB

Each time the PFC or PWM switches are turned on, a voltage spike occurs on the current sense resistor. To avoid faulty triggering, a leading-edge blanking time is built into the device. During the blanking period the current limit comparator is disabled and cannot switch off the gate driver.

#### VCC Pin Over-Voltage Protection – VCC OVP

The VCC OVP function is used to prevent device damage. If the  $V_{CC}$  voltage is higher than  $V_{CC-OVP}$  and lasts for a time  $t_{VCC-OVP}$ , the controller stops all switching operations and enters the latch mode until the AC plug is removed.

# Adjustable Over-Temperature Protection and External Protection Triggering – RT Pin

The RT pin is used to achieve over-temperature protection using an NTC resistor and provides external protection triggering for additional protection. Typically, since the external protection triggerig is usually used to protect the power system from abnormal conditions it needs a fast reaction speed or a short reaction time. Therefore, the protection debounce time of the external protection triggering is set to around 100µs once the RT pin voltage is lower than 0.5V. For over temperature protection, since the temperature cannot change rapidly, the protection debounce time should not be activated quickly. The protection debounce time for the OTP is set to around 10ms. In addition, to avoid improper triggering due to a lightning test, the RT pin triggering voltage of the OTP is set to 1.0V, which is higher than the external triggering voltage of 0.5V.

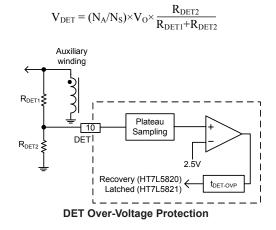

#### **DET Pin Over-Voltage Protection – DET OVP**

An output over-voltage protection is implemented by sensing the auxiliary winding voltage on the DET pin. The QR OVP works by sampling the plateau voltage on the DET pin after the PWM switch-off sequence. A 4 $\mu$ s internal blanking time guarantees a clean plateau provided that the leakage inductance ringing has been fully damped. If the sampled plateau voltage exceeds the OVP trip level of 2.5V and lasts for t<sub>DET-OVP</sub>, the device will enter auto-recovery protection (HT7L5820) or the latch mode (HT7L5821) until the AC power is removed. The protection voltage level can be determined by the ratio of the external resistor divider R<sub>DET1</sub> and R<sub>DET2</sub>, as shown in the following figure. The flat voltage on the DET pin can be expressed by the following equation:

#### **Output Open-Loop and Over-Load Protection**

To protect the circuit from being damaged during conditions of output open-loop or overload, the device includes an OLP function. Under such fault conditions, the output voltage is decreased and the sink current of the photo-coupler is reduced. This will force the FB pin voltage to increase using an internal bias. When the FB pin voltage ramps up to 4.2V for 50ms the OLP protection is activated to turn off the power switch and stop all switching operations.

### Package Information

Note that the package information provided here is for consultation purposes only. As this information may be updated at regular intervals users are reminded to consult the <u>Holtek website</u> for the latest version of the <u>package</u> information.

Additional supplementary information with regard to packaging is listed below. Click on the relevant section to be transferred to the relevant website page.

- Further Package Information (include Outline Dimensions, Product Tape and Reel Specifications)

- Packing Meterials Information

- Carton information

### 16-pin NSOP (150mil) Outline Dimensions

D

| Sumbol | Dimensions in inch |           |       |  |

|--------|--------------------|-----------|-------|--|

| Symbol | Min.               | Nom.      | Max.  |  |

| A      | —                  | 0.236 BSC | —     |  |

| В      | —                  | 0.154 BSC | —     |  |

| С      | 0.012              | —         | 0.020 |  |

| C'     | _                  | 0.390 BSC | —     |  |

| D      | _                  | —         | 0.069 |  |

| E      | _                  | 0.050 BSC | —     |  |

| F      | 0.004              | —         | 0.010 |  |

| G      | 0.016              | —         | 0.050 |  |

| Н      | 0.004              | —         | 0.010 |  |

| α      | 0°                 | —         | 8°    |  |

| Symbol | Dimensions in mm |           |      |  |  |

|--------|------------------|-----------|------|--|--|

| Symbol | Min.             | Nom.      | Max. |  |  |

| A      | _                | 6.000 BSC | _    |  |  |

| В      | _                | 3.900 BSC | —    |  |  |

| С      | 0.31             | —         | 0.51 |  |  |

| C'     | —                | 9.900 BSC | _    |  |  |

| D      | —                | —         | 1.75 |  |  |

| E      | _                | 1.270 BSC | _    |  |  |

| F      | 0.10             | —         | 0.25 |  |  |

| G      | 0.40             | —         | 1.27 |  |  |

| Н      | 0.10             | —         | 0.25 |  |  |

| α      | 0°               | _         | 8°   |  |  |

Copyright<sup>®</sup> 2016 by HOLTEK SEMICONDUCTOR INC.

The information appearing in this Data Sheet is believed to be accurate at the time of publication. However, Holtek assumes no responsibility arising from the use of the specifications described. The applications mentioned herein are used solely for the purpose of illustration and Holtek makes no warranty or representation that such applications will be suitable without further modification, nor recommends the use of its products for application that may present a risk to human life due to malfunction or otherwise. Holtek's products are not authorized for use as critical components in life support devices or systems. Holtek reserves the right to alter its products without prior notification. For the most up-to-date information, please visit our web site at http://www.holtek.com/en.